Основная плата STM32F030C8T6 минимальная системная основная STM32F030 мини плата.|Крышки

298,41 руб.

Новое поступление

Характеристики

*Текущая стоимость 6 483,36 уже могла изменится. Что бы узнать актуальную цену и проверить наличие товара, нажмите "Добавить в корзину"

| Месяц | Минимальная цена | Макс. стоимость | Цена |

|---|---|---|---|

| Feb-23-2026 | 8233.72 руб. | 8398.55 руб. | 8315.5 руб. |

| Jan-23-2026 | 6677.86 руб. | 6811.19 руб. | 6744 руб. |

| Dec-23-2025 | 8104.1 руб. | 8266.48 руб. | 8185 руб. |

| Nov-23-2025 | 8039.63 руб. | 8200.73 руб. | 8119.5 руб. |

| Oct-23-2025 | 6418.90 руб. | 6546.36 руб. | 6482 руб. |

| Sep-23-2025 | 7909.98 руб. | 8067.27 руб. | 7988 руб. |

| Aug-23-2025 | 7844.84 руб. | 8001.99 руб. | 7922.5 руб. |

| Jul-23-2025 | 7780.61 руб. | 7936.89 руб. | 7858 руб. |

Описание товара

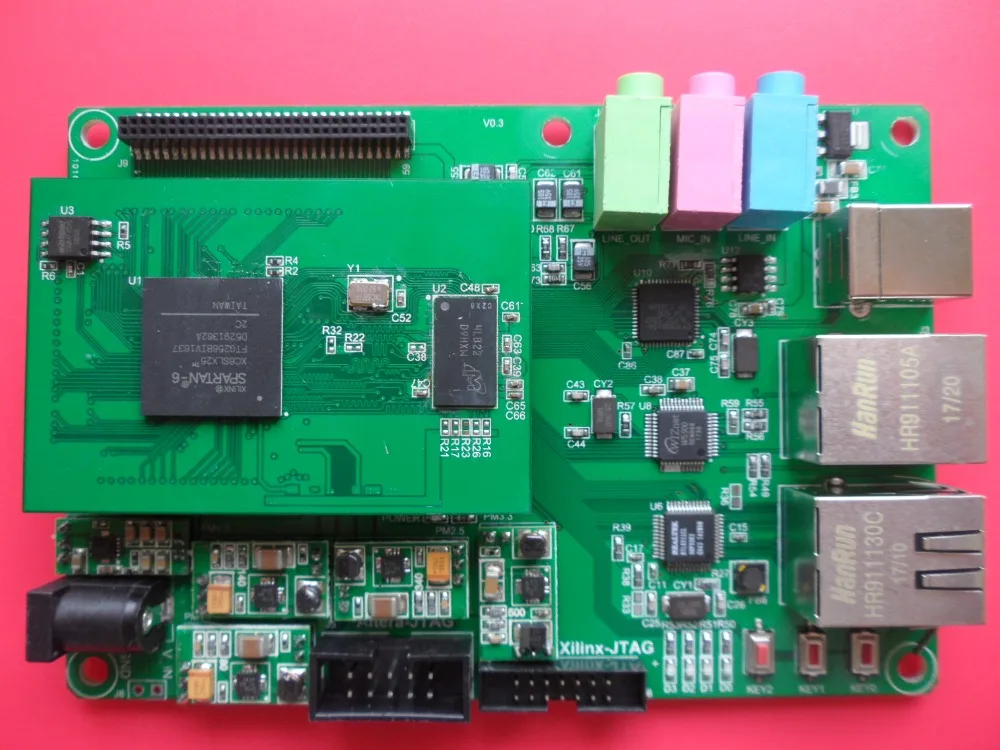

Без нагрузки расширительной пластины

Основная плата ресурсы:1. Ядро является чипом FPGA XC6SLX25-2FTG256.2. Чип конфигурации вспышки W25Q64BV, 8 мбайт памяти, также может использоваться для хранения данных пользователя.3. Гранулы памяти DDR3 MT41J64Mxx-15E, 1 Гбит (128 Мбайт) пространства для хранения, может поддерживать основную частоту 320 МГц.4. Поддержка режима конфигурации JTAG и SPI, где SPI совместим с режимом интерфейса x1, x2, X4.5. Активный кристаллический осциллятор 50 МГц на плате поддерживает пользователей, чтобы продлить время.6. Остальные 120 выдвижных пьедесталов IO могут образовывать 60 дифференциальных пар (LVDS).7. Поддержка 12 групп LVDS часов ввода/вывода.8. Позолоченное удлиненное основание, расстояние 1,27 мм, подходит для вторичного развития.Расширена плата ресурсы:1. 240PIN разъем может быть соединен с различными видами FPGA розеток в нашем магазине.2. TI силовой модуль TPS62130, 3,3 V/2,5 V/1,5 V/1,2 V напряжения.3. Модуль питания TI TPS51200, Справочное напряжение DDR, ингаляция тока и всасывание (раковина и источник).4. Поддержка стандартного JTAG интерфейса загрузки Altera и Xilinx.5. Чип USB 2,0 CY7C68013A поддерживает высокоскоростной режим 480 Мбит/с и интерфейс GPIF.6. Чип Ethernet W5500 поддерживает 100 Мбит/с, протокол TCP/IP/UDP и интерфейс SPI.7. Чип Ethernet RTL821CL поддерживает 1000 Мбит/с, интерфейс RGMII.8. Аудио чип WM8731, 24 бит ADC/DAC, 96 кбит/с, интерфейс IIS.9. Пользовательский IO Расширенный разъем 2*30 PIN.10. Разъем для sd-карты 1, кнопка 3, светодиодный светильник 4.

Смотрите так же другие товары: