Новое поступление

Модуль MFRC522 карта RFID IC модуль чтения и записи интерфейс UART/SPI/I2C большое расстояние

Wifi Плата расширения OpenMV3 2Cam M7 беспроводная видео Atwinc 1500|Крышки переключателей| |

Регулятор температуры компрессора HD 060 контроллер шкафа Холодильный

SIM7600E Φ LTE модуль поддерживает функцию GPS.|Крышки переключателей| |

Bluetooth 4.04.1 сканирование адресов MAC с USB на последовательный выход зонд для

Новая промышленная изоляция 4 ходовой концентратор RS485 усиленное устройство для

Pd2.02.0pps/QC2.0QC3.0QC4/AFC/FCP/SCP/MTK/SFCP проверка быстрой зарядки|Крышки переключателей| |

Характеристики

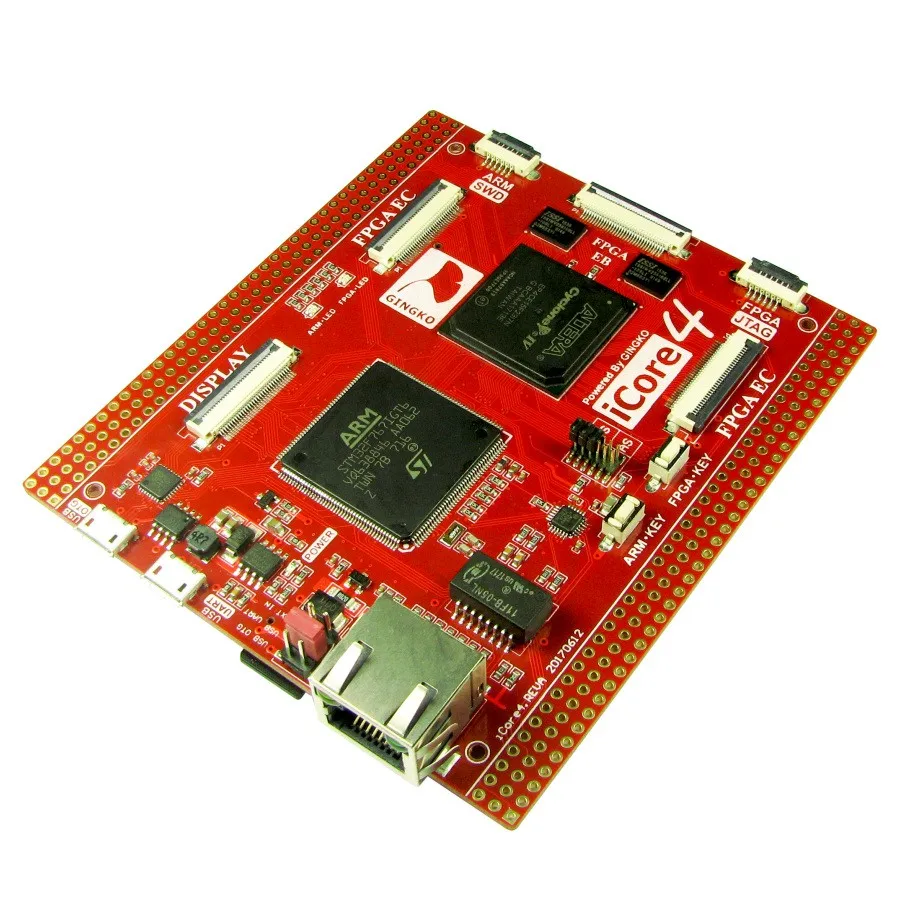

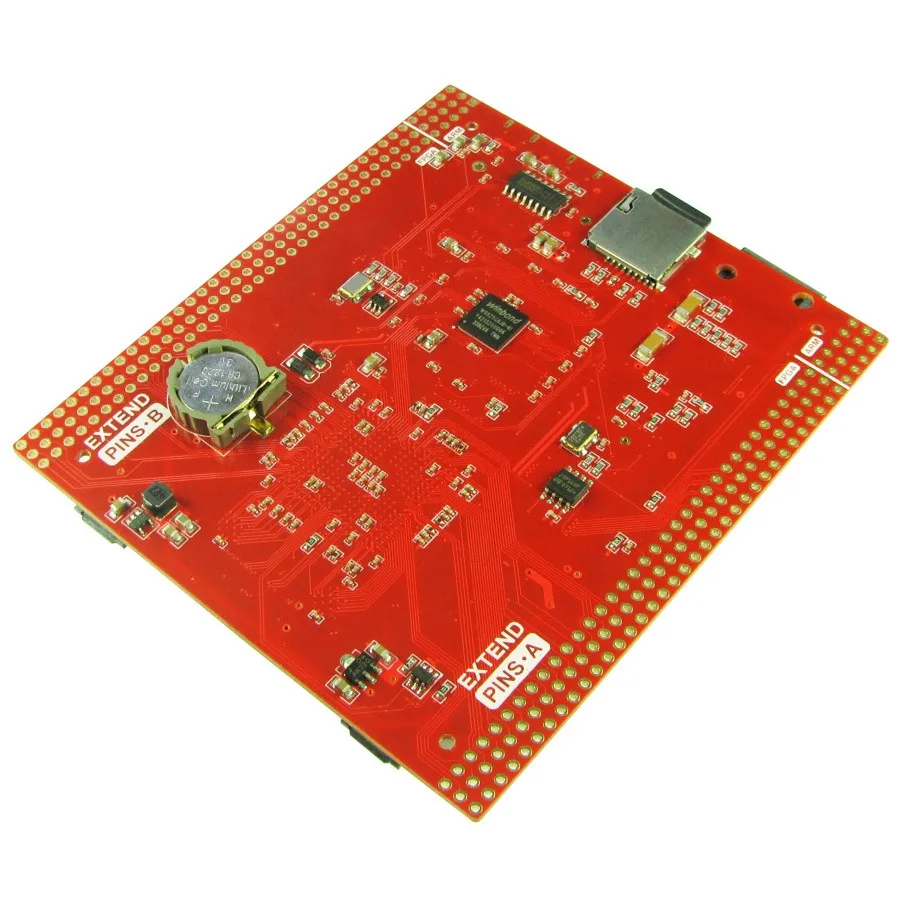

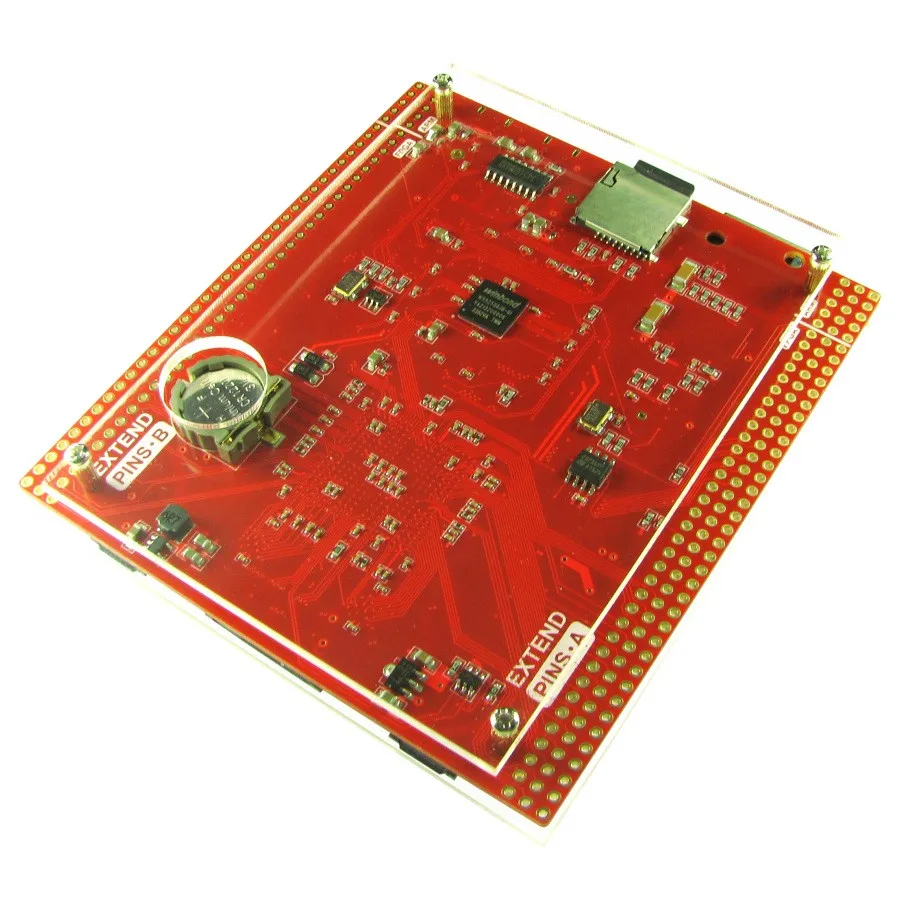

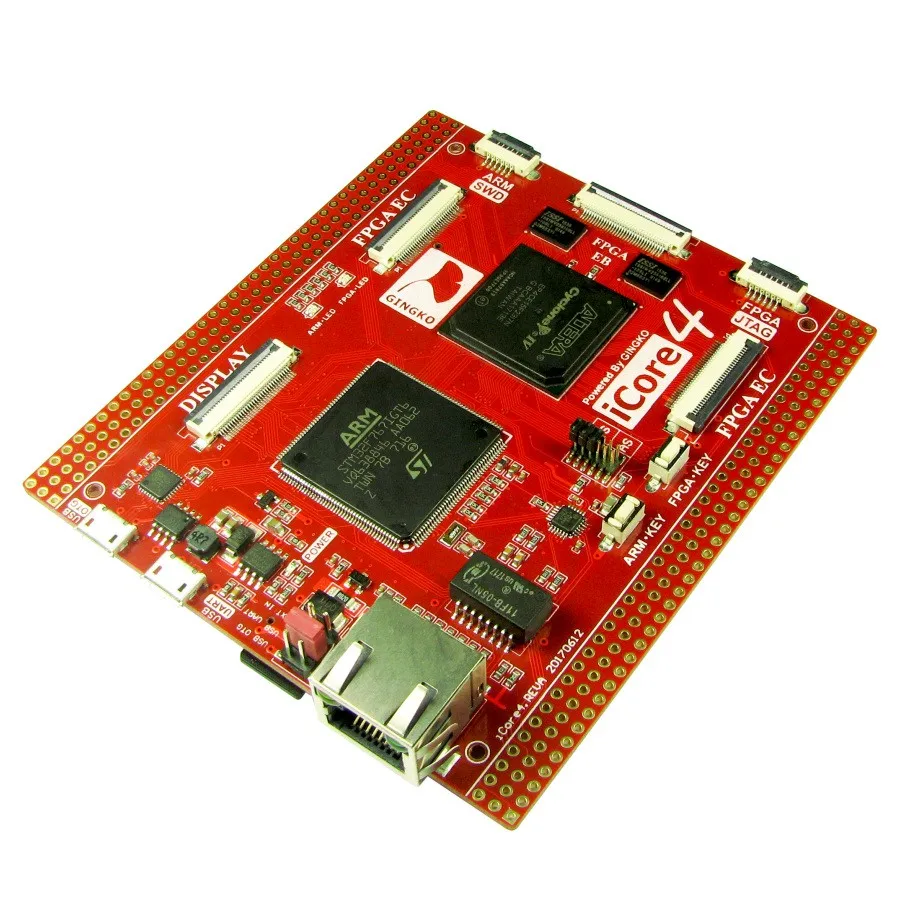

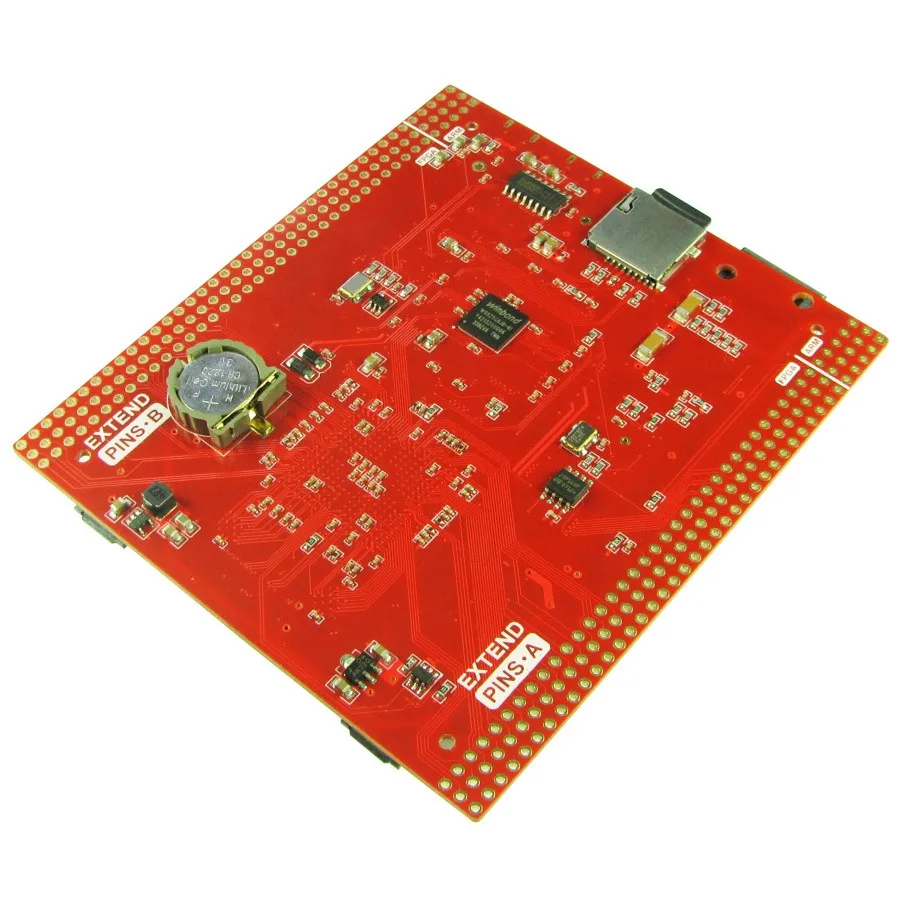

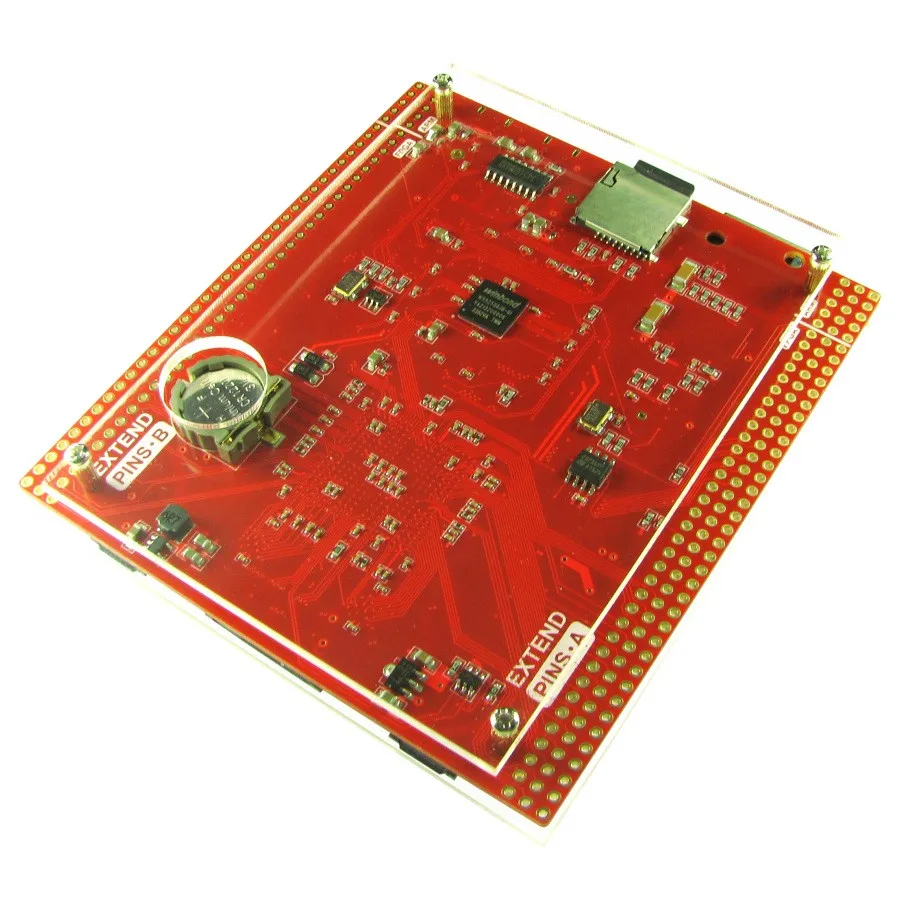

ICore4 ARM FPGA двухъядерный промышленный контроллер макетная плата STM32 FPGA|Крышки

История изменения цены

*Текущая стоимость 9 566,19 - 10 392,18 уже могла изменится. Что бы узнать актуальную цену и проверить наличие товара, нажмите "Добавить в корзину"

| Месяц | Минимальная цена | Макс. стоимость | Цена |

|---|---|---|---|

| Mar-22-2026 | 11384.16 руб. | 11953.21 руб. | 11668.5 руб. |

| Feb-22-2026 | 11288.59 руб. | 11852.42 руб. | 11570 руб. |

| Jan-22-2026 | 9470.6 руб. | 9944.84 руб. | 9707 руб. |

| Dec-22-2025 | 11097.55 руб. | 11652.5 руб. | 11374.5 руб. |

| Nov-22-2025 | 9662.78 руб. | 10145.65 руб. | 9903.5 руб. |

| Oct-22-2025 | 10905.40 руб. | 11450.78 руб. | 11177.5 руб. |

| Sep-22-2025 | 10810.8 руб. | 11351.63 руб. | 11080.5 руб. |

| Aug-22-2025 | 10714.85 руб. | 11250.1 руб. | 10982 руб. |

| Jul-22-2025 | 10618.99 руб. | 11149.19 руб. | 10883.5 руб. |

Описание товара

Отличная производительность, практичная двухъядерная промышленная карта управления, шокирующий выпуск!

Разница между промышленным и промышленным уровнем quasi:

![]()

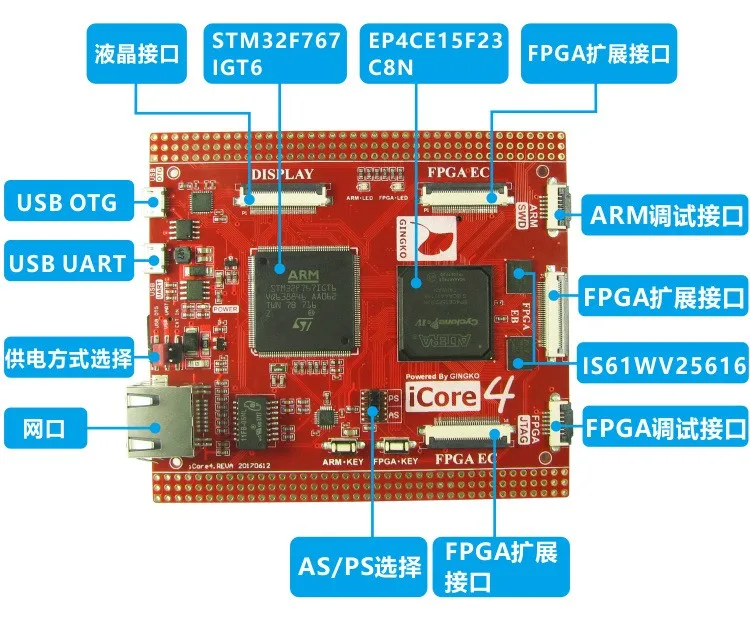

Один, технические индикаторы:

1, ARM + FPGA, двухъядерный, новая комбинация, сильный контакт;

2. ARM выбирает высокопроизводительную модель M7, модель STM32F767IGT6.176 средства ухода за кожей стопЕсть много средств.

3. FPGA выбирает EP4CE15F23C8N серии cycloeiv.484 средства ухода за кожей стоп;

4, печатная плата-это шесть слоев печатной платы;

5, расширение руки32 Мб SDRAM (синхронное динамическое ОЗУ)Он может использоваться в качестве дисплея буфера.

6, расширение FPGAС двумя ЧИПАМИ 61WV25616(Рабочая частота 100 м, размер 512KB) используется для работы в пинг-понге; Это очень практично.

7, ПЛИСДвойные часыВход, 24 м/25 м, более удобный в использовании;

8, встроенный в USB-TTL, непосредственно подключенный к компьютеру, может отображать информацию о задержке;

9, 100 м Высокоскоростной Ethernet;

10, USB2.0 высокоскоростной USB 2 OTG интерфейс, скорость до40 МбВыше; Также можно читать U диск;

11. ПоддержкаРука Настройка ПЛИСОн также может поддерживать удаленную настройку FPGA через Ethernet, USB, tf-карту и так далее.

12. С собственным интерфейсом драйвера дисплея, он поддерживает четыре точки, три дюйма, 5 дюймов, 7 дюймов, экран с передачей; Большая поддержка разрешения составляет 1024x768;

13, до 200 + интерфейсов FPGA IO;

14. Встроенная цепь контроля тока и напряжения.

Нанесите наICore4Основная платаМодульная:

ICore4 основные процедуры экспериментов

| Серийный номер | Рука обычные[Обновление]... | FPGA обычные[Обновление]... |

| 1 | Стандартный один: ручной привод, трехцветный светодиодный | Стандартный: GPIO выход эксперимента-светильник светодиодный |

| 2 | Стандартный номер 2: читает состояние кнопки ARM | Режим 2: Ввод GPIO, Ввод Ключа распознавания экспериментов |

| 3 | Три рутины: EXTI interrubber extivation-кнопка чтения | Рутинная тройка: счетчик-эксперимент, использование счетчика |

| 4 | 4: USART experiment-светодиодный пульт управления | 4. Стандартный сигнал TapII-анализатор логики |

| 5 | Стандартный номер 5: светодиодный таймер с таймером, таймером и таймером | Стандартный пять: базовый эксперимент с логическими воротами, использование логических ворот |

| 6 | Стандартный номер 6: IWDG watchdog experiment - reset ARM | Стандартный 6: сигнал TapII-анализатор логики |

| 7 | Режим seven: WWDG watchdog experiment - reset ARM | Обычная семь: базовый эксперимент с логическими воротами-использование логических ворот |

| 8 | Стандартный Восьмиядерный: Таймер PWM, экспериментальная дышащая лампа | Стандартный Восьмиядерный: эксперимент с мультипликатором, использование мультипликатора |

| 9 | Стандартный номер: эксперимент с ADC, контроль мощности | Вторая версия: цикл экспериментов с блокировкой фаз, цикл с блокировкой фаз |

| 10 | Режим 10: Время и дата в режиме реального времени | Рутинная десять: FSMC эксперимент по связям с шинами-Режим многократного адреса |

| 11 | Стандартный десять один: DMA эксперимент-память для передачи памяти | Стандартный десять один: Эксперимент FSMC с автобусной связью, режим автономной адресной связи |

| 12 | Стандартный десять двух: эксперимент с общим таймером, светодиодный светильник с обычными интервалами | Рутинная десять двух: эксперименты на базе UART ARM и FPGA |

| 13 | Три рутины: SDIO experience-Чтение информации о sd-карте | Рутинная десять три: эксперименты на основе SPI ARM и FPGA |

| 14 | Четырёхъядерный: FATFS experience-управление файлами | 14: эксперимент по связи между ARM и FPGA, основанный на I2C |

| 15 | Обычная пятнадцать: USB_CDC эксперимент-Высокоскоростная передача данных | Обычная пятнадцать: ARM + FPGA эксперимент по хранения данных, основанный на однопортовой ОЗУ |

| 16 | Стандартный 16: USB_HID эксперимент-двунаправленный передача данных | Стандартный 16: ARM + FPGA эксперимент по хранения данных, основанный на ОЗУ с двойным портом |

| 17 | Стандартный seventeen: USB_MSC эксперимент-чтение/запись U диска (большая память емкости) | Стандартный эксперимент seventeen: ARM + FPGA, доступ к данным, основанный на FIFO |

| 18 | Стандартный 18: USB_VCP эксперимент-виртуальный последовательный порт | Примечания |

| 19 | Стандартный 19: USBD_MSC эксперимент-виртуальный U диск | Экспериментальная обычные Описание |

| 20 | Две версии: lwip_tcp_клиентский эксперимент-передача данных Ethernet | |

| 21 | Рутинные два десятых одного: lwip_tcp_серверный эксперимент-передача данных Ethernet | |

| 22 | 2. 10, 2: LWIP_UDP эксперимент-передача данных Ethernet | |

| 23 | Рутинные два десятых трех: lwip_http-эксперимент -- веб-сервер | |

| 24 | 2. Четырнадцать: Эксперимент LWIP_DHCP-динамическое распределения IP | |

| 25 | Две пятнадцать: Эксперимент LWIP_DNS-разрешение домена | |

| 26 | Обычное два шестнадцать: LWIP_MODBUS_TCP эксперимент-контроль мощности | |

| 27 | Стандартный 2 seventeen: LWIP_NETIO эксперимент-измерение скорости Ethernet | |

| 28 | Стандартный два 18: эксперимент FMC-чтение и запись FPGA | |

| 29 | Две версии 19: SD_IAP_FPGA, эксперимент -- обновление и обновление FPGA | |

| 30 | Три версии 10: U_DISK_IAP_FPGA, эксперимент, обновление и обновление FPGA | |

| 31 | Стандартный три десятых: HTTP_IAP_FPGA эксперимент-обновление и обновление FPGA | |

| 32 | Три десятых двух: эксперимент UART_IAP_ARM-обновление и обновление STM32 | |

| 33 | Три версии: SD_IAP_ARM, эксперимент-обновление и обновление STM32 | |

| 34 | Стандартный три четырнадцать: U_DISK_IAP_ARM experiment-обновление и обновление STM32 | |

| 35 | Стандартный три пятнадцать: HTTP_IAP_ARM эксперимент-обновление и обновление STM32 | |

| 36 | Стандартный три шестнадцать: эксперимент DAC-выходное напряжение постоянного тока | |

| 37 | Стандартный 3, 17: SDRAM эксперимент-чтение и письмо SDRAM | |

| 38 | Стандартный тест трех восемнадцать: DSP MATH library test | |

| Примечания | Readme |

![]()

![]()

![]()

![]()

Смотрите так же другие товары: